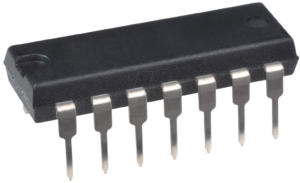

Statisches 8-stufiges CMOS-VerschieberegisterBeschreibungBei den Typen CD4014B und CD4021B handelt es sich um 8-stufige Register mit parallelen oder seriellen Eingängen und seriellen Ausgängen, die gemeinsame Eingänge zur UHRZEIT- und PARALLEL-/SERIENSTEUERUNG, einen einzigen SERIELLEN Dateneingang und individuelle parallele “JAM“-Eingänge für jede Registerstufe haben. Jede Registerstufe ist ein Master-Slave-Flip-Flop vom Typ D. Zusätzlich zu einer Ausgangsform der Stufe 8 sind auch “Q“-Ausgänge von den Stufen 6 und 7 verfügbar. Sowohl die parallele als auch die serielle Eingabe in das Register erfolgt synchron mit dem positiven Taktleitungsübergang im CD4014B. Im CD4021B erfolgt die serielle Eingabe synchron mit dem Takt durch die parallele Eingabe asynchron. Bei beiden Typen wird die Eingabe durch den PARALLEL/SERIAL CONTROL-Eingang gesteuert. Wenn der PARALLEL/SERIAL CONTROL-Eingang niedrig ist, werden die Daten seriell in das 8-stufige Register synchron mit dem positiven Übergang der Taktleitung verschoben. Wenn der Eingang PARALLEL-/SERIENSTEUERUNG auf High liegt, werden die Daten über die parallelen Eingangsleitungen und synchron mit dem positiven Übergang der Taktleitung in das 8-stufige Register gestaut. Beim CD4021B wird der CLOCK-Eingang der internen Stufe “erzwungen“, wenn ein asynchroner Paralleleingang erfolgt. Eine Registererweiterung über mehrere Pakete ist zulässig. Die Typen der Serien CD4014B und CD4021B werden in 16-poligen hermetischen Dual-in-Line-Keramikgehäusen (Suffix F3A), 16-poligen Dual-in-Line-Kunststoffgehäusen (Suffix E), 16-poligen Small-Outline-Gehäusen (Suffixe M, M96, MT und NSR) und 16-poligen Thin-Shrink Small-Oultine-Gehäusen (Suffixe PW und PWR) geliefert.Merkmale• Betrieb bei mittlerer Geschwindigkeit…12 MHz (typ.) Taktfrequenz bei VDD – VSS = 10 V• Vollständig statischer Betrieb• 8 Master-Slave-Flipflops plus Ausgangspufferung und Steuertor• 100% geprüft auf Ruhestrom bei 20 V• Maximaler Eingangsstrom von 1 µA bei 18 V über den gesamten Gehäuse-Temperaturbereich; 100 nA bei 18 V und 25°C• Rauschabstand (voller Paket-Temperaturbereich) = 1 V bei VDD = 5 V 2 V bei VDD = 10 V 2,5 V bei VDD = 15 V• Standardisierte, symmetrische Ausgangskennlinien• Parametrische Nennwerte von 5 V, 10 V und 15 V• Erfüllt alle Anforderungen des JEDEC Tentative Standard Nr. 13B, “Standard Specifications for Description of ‚B‘ Series CMOS Devices“.Anwendungen• Parallele Eingabe-/Serielle Ausgabe-Datenwarteschlange• Parallel zur seriellen Datenkonvertierung• Allzweck-Register

CD 4021BE TEX – CMOS 8-Stage Static Shift Register, 3 … 18 V, DIL-16

0,53 €

- Lieferzeit: 1-2 Werktage

- ab Lager